О.М. Брехов, М.О. Ратников

10

можно будет сделать выводы о типе нарушения работы системы

(сбой или отказ).

Реализация тестового функционального описания развернутого

генератора CRC.

В качестве примера реализации тестового функци-

онального описания рассмотрим реализацию конвейера с разверну-

тым алгоритмом генерации контрольного кода CRC. Для исходных

кодов тестовой системы был использован язык описания и верифика-

ции аппаратного обеспечения SystemVerilog 2005 (IEEE 1800-2005)

[6]. Результаты синтеза с помощью пакета Mentor Graphics Precision

Synthesis представлены в табл. 1.

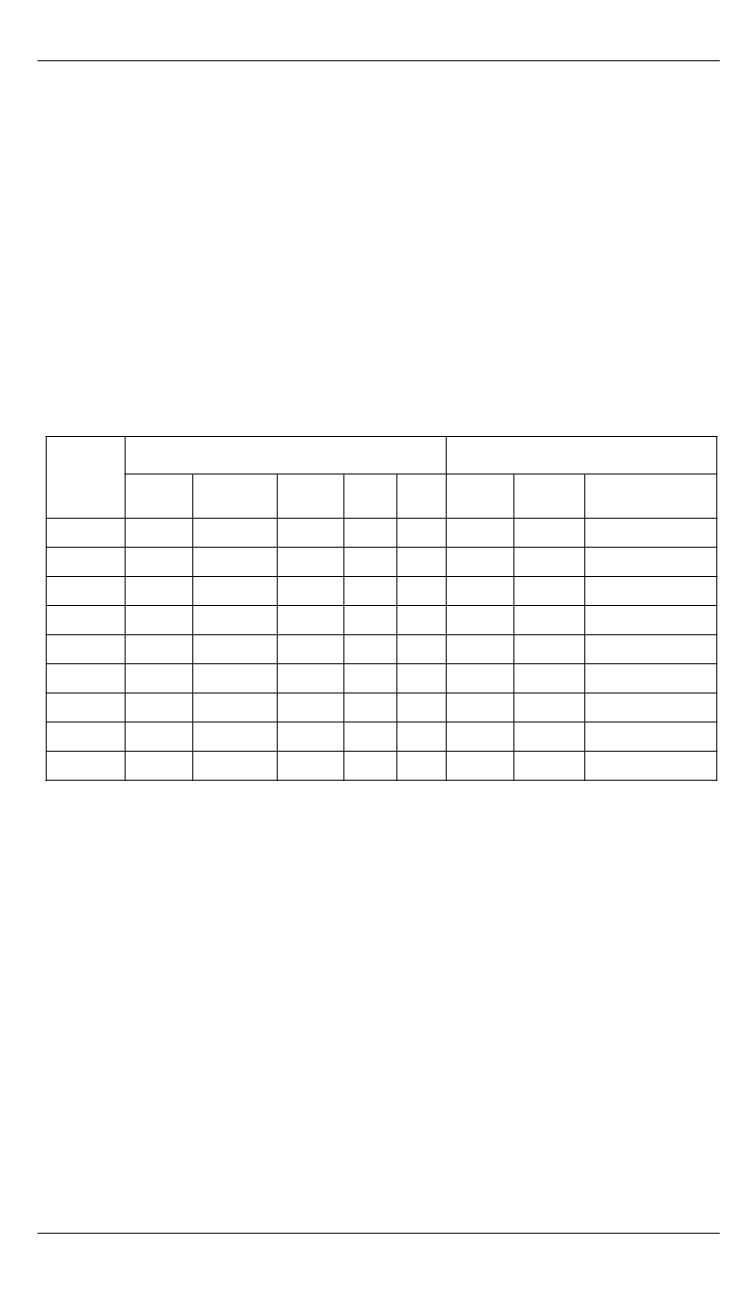

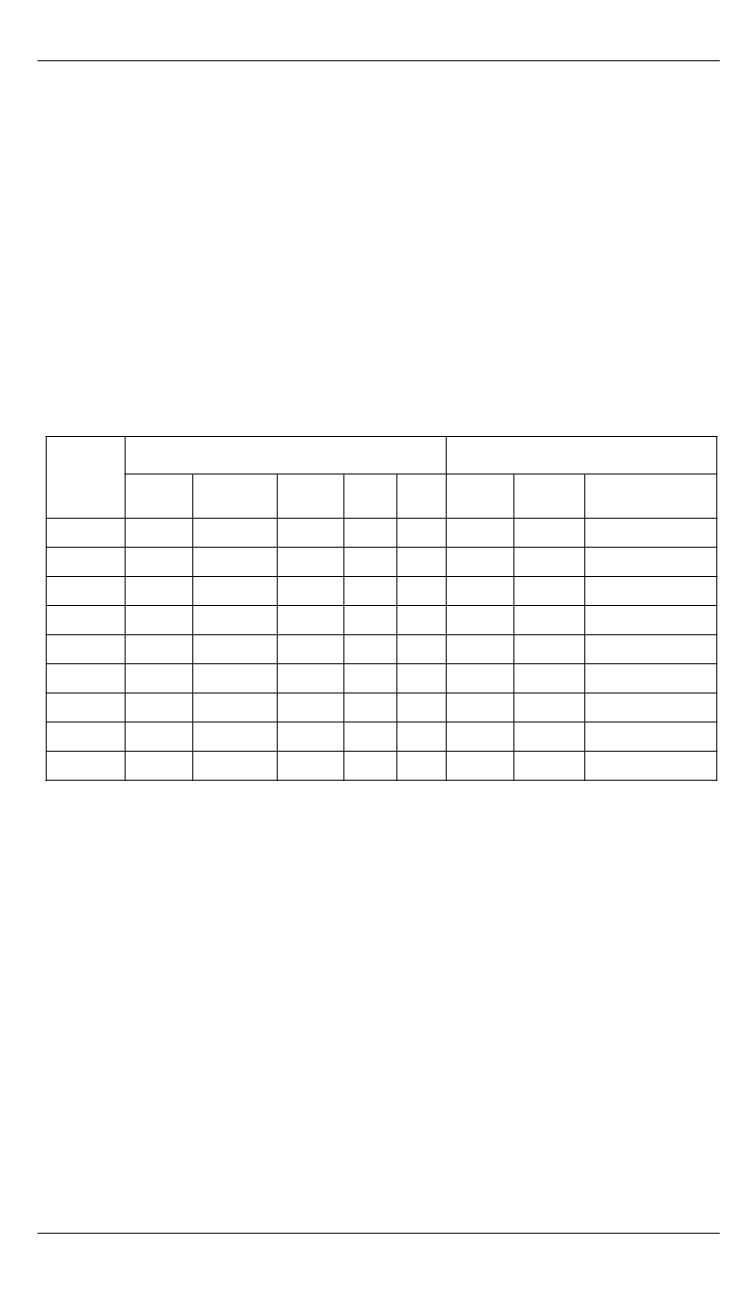

Таблица 1

Результаты синтеза развернутого генератора CRC

Количе-

ство

ступеней

В базис ПЛИС Altera Stratix

В базис ПЛИС Xilinx Virtex

Занято

ячеек

Частота,

МГц

nets

LCs Inst. LUTs

CLB

Частота,

МГц

100

765 925,926 794 765 784 271

382

698,324

200

1565 819,672 1594 1565 1584 571

782

677,507

300

2365 819,672 2394 2365 2384 871

1182

663,570

400

3165 819,672 3194 3165 3184 1171 1582

663,570

500

3965 819,672 3994 3965 3984 1471 1982

663,570

600

4765 819,672 4794 4765 4784 1771 2382

663,570

700

5565 819,672 5594 5565 5584 2071 2782

663,570

800

6365 819,672 6394 6365 6384 2371 3182

663,570

900

7165 819,672 7194 7165 7184 2671 3582

663,570

Для двух ПЛИС от разных производителей система продемон-

стрировала идентичные результаты: монотонное увеличение количе-

ства занятых ресурсов при увеличении количества ступеней конвейе-

ра. Максимальная частота работы системы близка к максимально

возможной для соответствующей модели ПЛИС. Это подтверждает

выполнение требования масштабируемости.

2.2.

Тестовая система на основе конвейеризированного гене-

ратора кода Хэмминга.

В качестве примера реализации тестового

функционального описания с определением места выявления сбоя

рассмотрим реализацию конвейера с развернутым алгоритмом гене-

рации кода Хэмминга, выявляющего две ошибки и исправляющего

одну ошибку.

Каждая из стадий конвейера в такой тестовой системе обрабаты-

вает один бит входного потока. В целях сохранения простоты вычис-

ления эталонного значения и упрощения верификации тестовой про-